This image below shows the internal design of a 4bit Magnitu

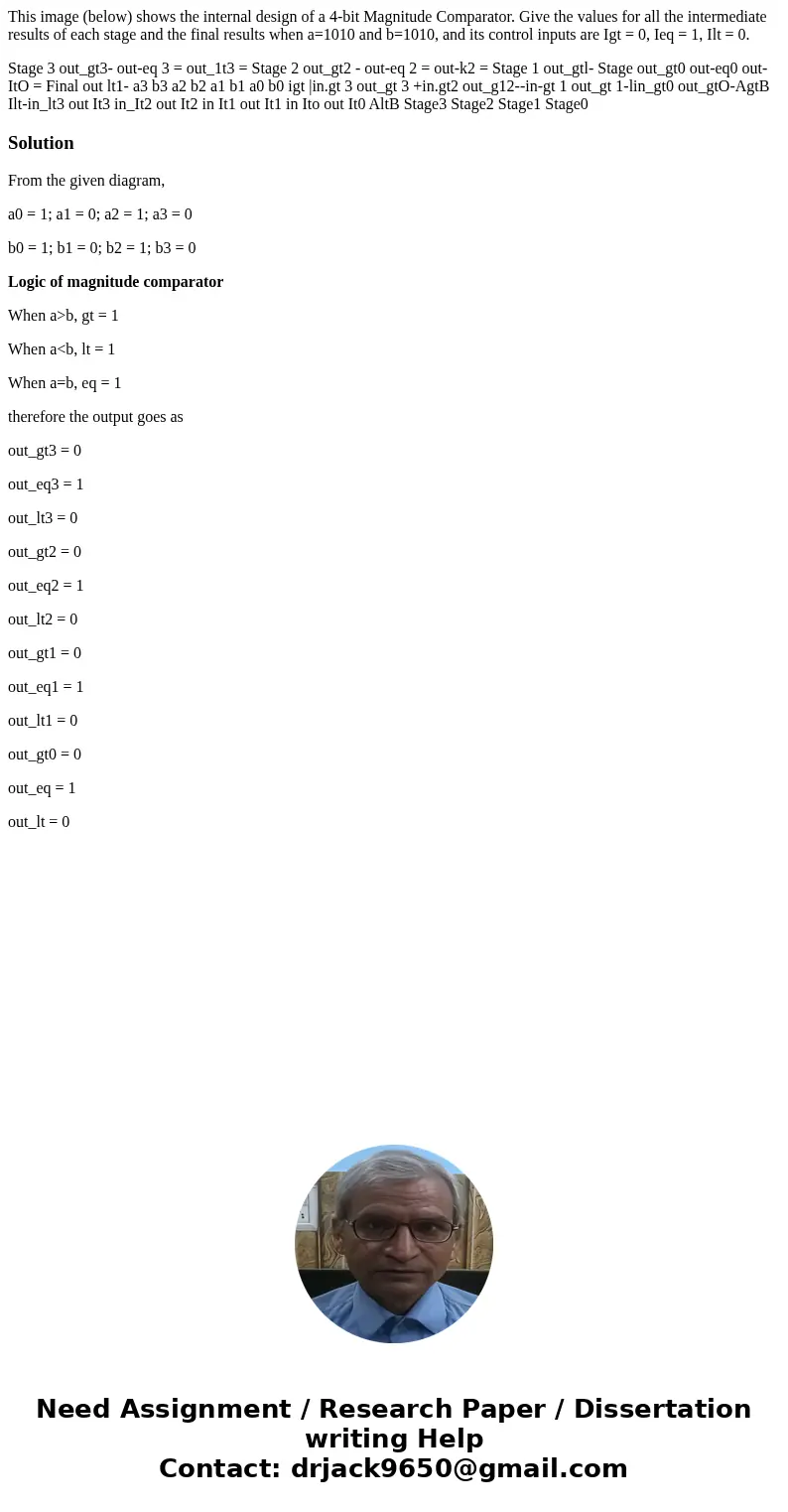

This image (below) shows the internal design of a 4-bit Magnitude Comparator. Give the values for all the intermediate results of each stage and the final results when a=1010 and b=1010, and its control inputs are Igt = 0, Ieq = 1, Ilt = 0.

Stage 3 out_gt3- out-eq 3 = out_1t3 = Stage 2 out_gt2 - out-eq 2 = out-k2 = Stage 1 out_gtl- Stage out_gt0 out-eq0 out-ItO = Final out lt1- a3 b3 a2 b2 a1 b1 a0 b0 igt |in.gt 3 out_gt 3 +in.gt2 out_g12--in-gt 1 out_gt 1-lin_gt0 out_gtO-AgtB Ilt-in_lt3 out It3 in_It2 out It2 in It1 out It1 in Ito out It0 AltB Stage3 Stage2 Stage1 Stage0Solution

From the given diagram,

a0 = 1; a1 = 0; a2 = 1; a3 = 0

b0 = 1; b1 = 0; b2 = 1; b3 = 0

Logic of magnitude comparator

When a>b, gt = 1

When a<b, lt = 1

When a=b, eq = 1

therefore the output goes as

out_gt3 = 0

out_eq3 = 1

out_lt3 = 0

out_gt2 = 0

out_eq2 = 1

out_lt2 = 0

out_gt1 = 0

out_eq1 = 1

out_lt1 = 0

out_gt0 = 0

out_eq = 1

out_lt = 0

Homework Sourse

Homework Sourse