How would you amend the following vhdl code so that when swi

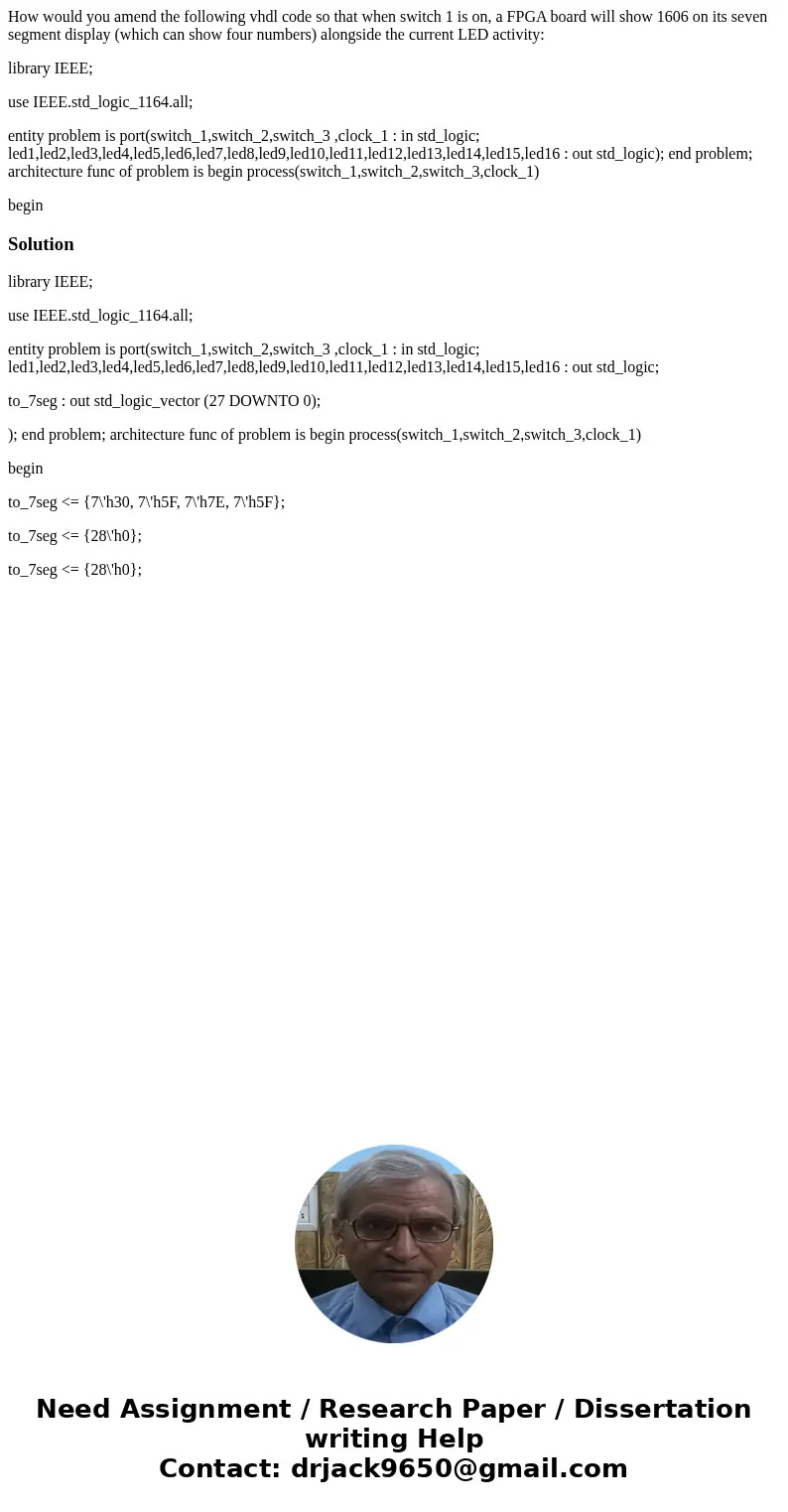

How would you amend the following vhdl code so that when switch 1 is on, a FPGA board will show 1606 on its seven segment display (which can show four numbers) alongside the current LED activity:

library IEEE;

use IEEE.std_logic_1164.all;

entity problem is port(switch_1,switch_2,switch_3 ,clock_1 : in std_logic; led1,led2,led3,led4,led5,led6,led7,led8,led9,led10,led11,led12,led13,led14,led15,led16 : out std_logic); end problem; architecture func of problem is begin process(switch_1,switch_2,switch_3,clock_1)

begin

Solution

library IEEE;

use IEEE.std_logic_1164.all;

entity problem is port(switch_1,switch_2,switch_3 ,clock_1 : in std_logic; led1,led2,led3,led4,led5,led6,led7,led8,led9,led10,led11,led12,led13,led14,led15,led16 : out std_logic;

to_7seg : out std_logic_vector (27 DOWNTO 0);

); end problem; architecture func of problem is begin process(switch_1,switch_2,switch_3,clock_1)

begin

to_7seg <= {7\'h30, 7\'h5F, 7\'h7E, 7\'h5F};

to_7seg <= {28\'h0};

to_7seg <= {28\'h0};

Homework Sourse

Homework Sourse