Assume we have a computer where the CPI1 when all memory acc

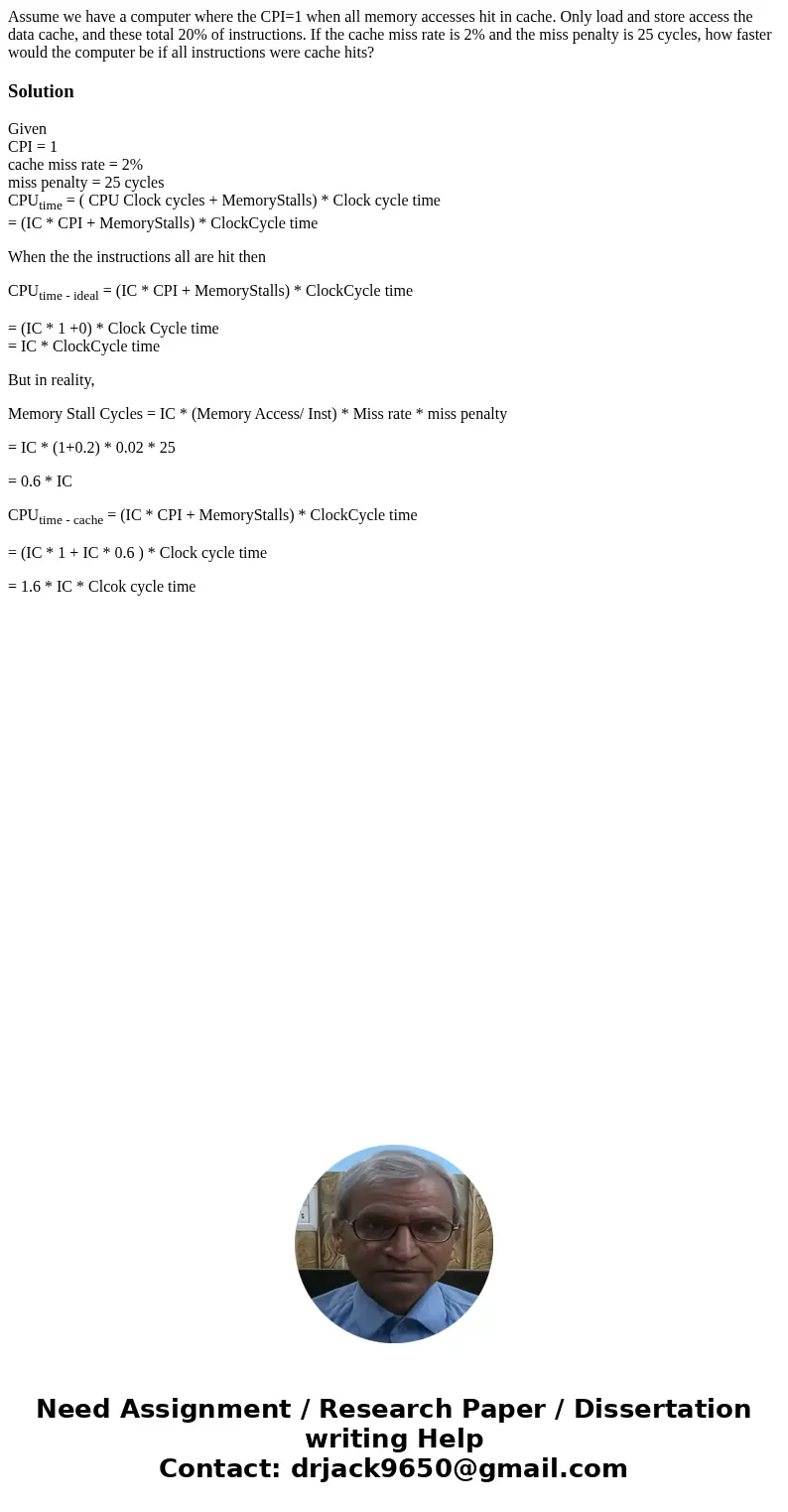

Assume we have a computer where the CPI=1 when all memory accesses hit in cache. Only load and store access the data cache, and these total 20% of instructions. If the cache miss rate is 2% and the miss penalty is 25 cycles, how faster would the computer be if all instructions were cache hits?

Solution

Given

CPI = 1

cache miss rate = 2%

miss penalty = 25 cycles

CPUtime = ( CPU Clock cycles + MemoryStalls) * Clock cycle time

= (IC * CPI + MemoryStalls) * ClockCycle time

When the the instructions all are hit then

CPUtime - ideal = (IC * CPI + MemoryStalls) * ClockCycle time

= (IC * 1 +0) * Clock Cycle time

= IC * ClockCycle time

But in reality,

Memory Stall Cycles = IC * (Memory Access/ Inst) * Miss rate * miss penalty

= IC * (1+0.2) * 0.02 * 25

= 0.6 * IC

CPUtime - cache = (IC * CPI + MemoryStalls) * ClockCycle time

= (IC * 1 + IC * 0.6 ) * Clock cycle time

= 1.6 * IC * Clcok cycle time

Homework Sourse

Homework Sourse