Divisor 4 bits LU Shift right Shift left Control test Remai

Solution

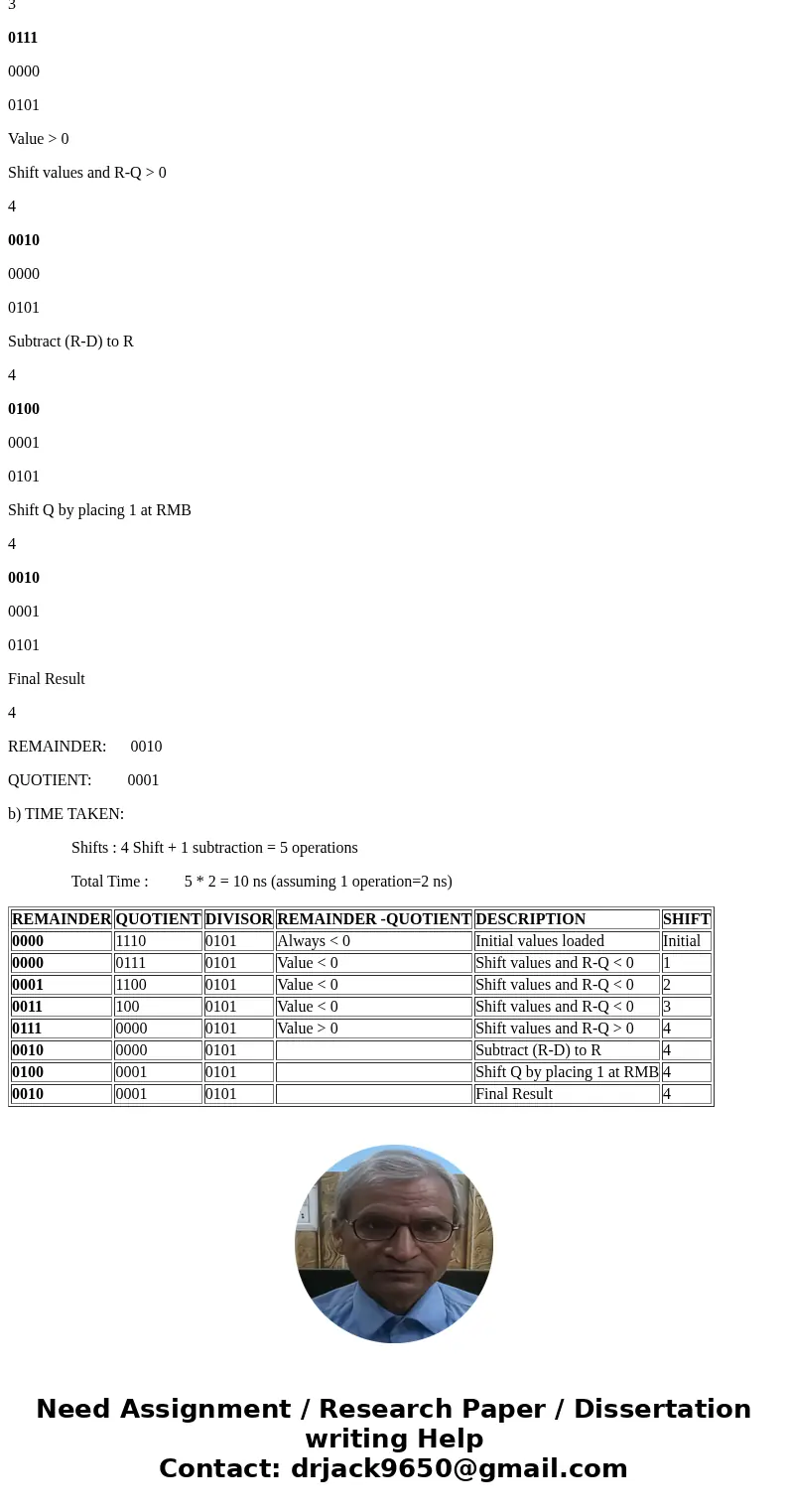

According to above Hardware, we are not using any other register to store quotient. The remainder is taken 8 bits and it is considered as both quotient and remainder

Steps for the Process:

i.Then Go to step 4

i.Then Go to step 8

i.e., First 4 bits is remainder(R) and next 4 bits is quotient (Q)

REMAINDER

QUOTIENT

DIVISOR

REMAINDER -QUOTIENT

DESCRIPTION

SHIFT

0000

1110

0101

Always < 0

Initial values loaded

Initial

0000

0111

0101

Value < 0

Shift values and R-Q < 0

1

0001

1100

0101

Value < 0

Shift values and R-Q < 0

2

0011

100

0101

Value < 0

Shift values and R-Q < 0

3

0111

0000

0101

Value > 0

Shift values and R-Q > 0

4

0010

0000

0101

Subtract (R-D) to R

4

0100

0001

0101

Shift Q by placing 1 at RMB

4

0010

0001

0101

Final Result

4

REMAINDER: 0010

QUOTIENT: 0001

b) TIME TAKEN:

Shifts : 4 Shift + 1 subtraction = 5 operations

Total Time : 5 * 2 = 10 ns (assuming 1 operation=2 ns)

| REMAINDER | QUOTIENT | DIVISOR | REMAINDER -QUOTIENT | DESCRIPTION | SHIFT |

| 0000 | 1110 | 0101 | Always < 0 | Initial values loaded | Initial |

| 0000 | 0111 | 0101 | Value < 0 | Shift values and R-Q < 0 | 1 |

| 0001 | 1100 | 0101 | Value < 0 | Shift values and R-Q < 0 | 2 |

| 0011 | 100 | 0101 | Value < 0 | Shift values and R-Q < 0 | 3 |

| 0111 | 0000 | 0101 | Value > 0 | Shift values and R-Q > 0 | 4 |

| 0010 | 0000 | 0101 | Subtract (R-D) to R | 4 | |

| 0100 | 0001 | 0101 | Shift Q by placing 1 at RMB | 4 | |

| 0010 | 0001 | 0101 | Final Result | 4 |

Homework Sourse

Homework Sourse