Write the verilog implementation of a half adder using behav

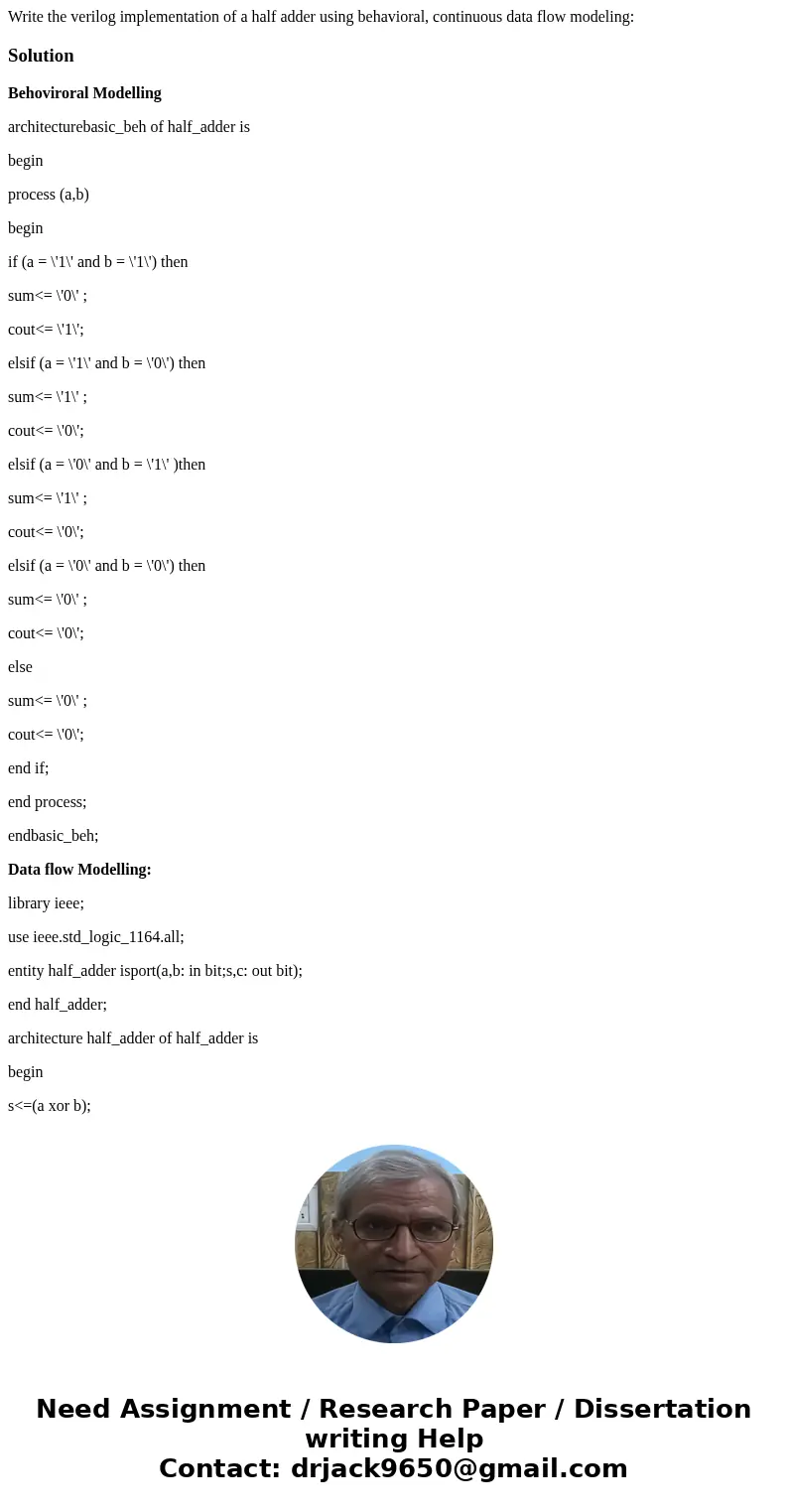

Write the verilog implementation of a half adder using behavioral, continuous data flow modeling:

Solution

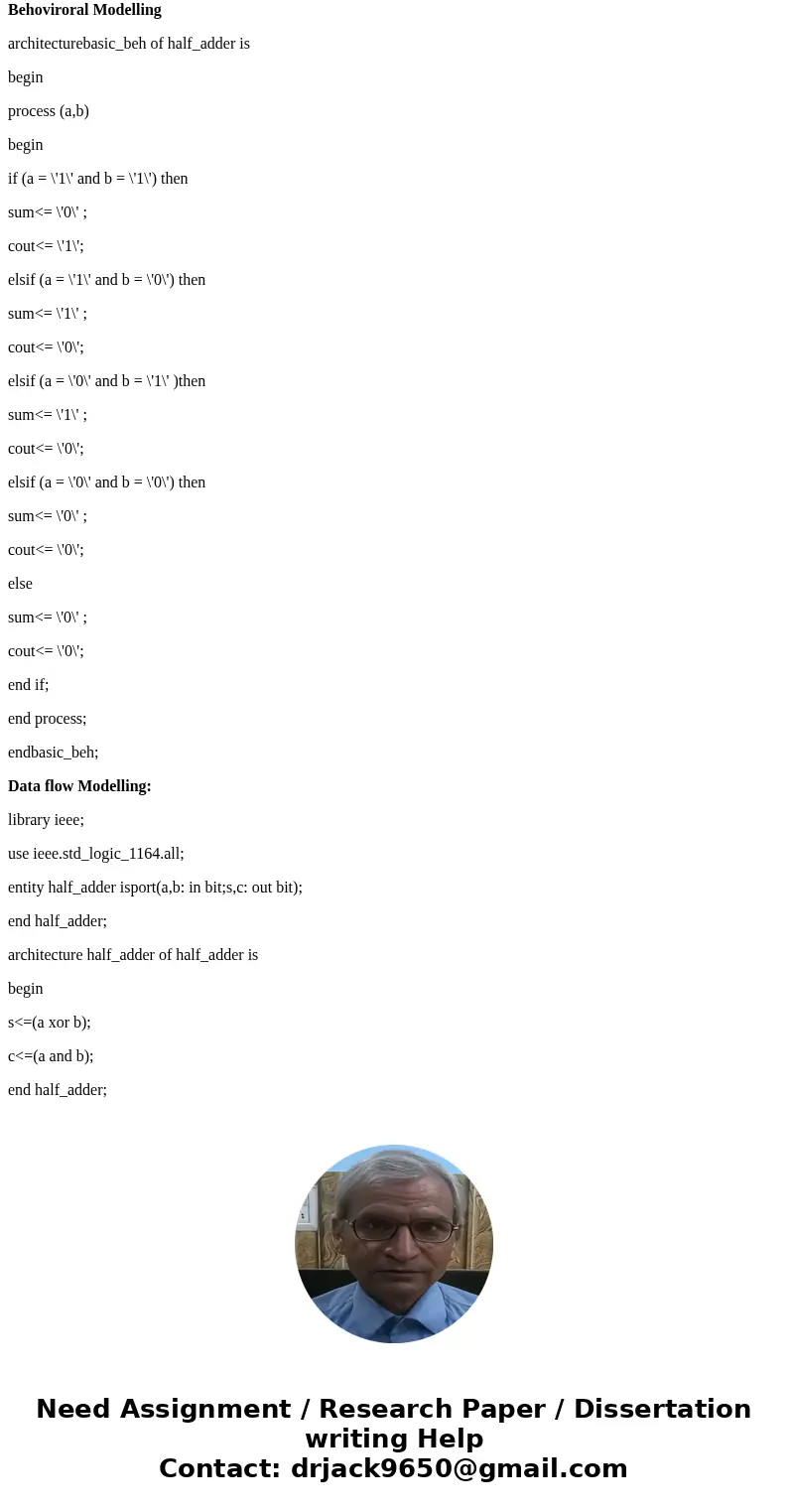

Behoviroral Modelling

architecturebasic_beh of half_adder is

begin

process (a,b)

begin

if (a = \'1\' and b = \'1\') then

sum<= \'0\' ;

cout<= \'1\';

elsif (a = \'1\' and b = \'0\') then

sum<= \'1\' ;

cout<= \'0\';

elsif (a = \'0\' and b = \'1\' )then

sum<= \'1\' ;

cout<= \'0\';

elsif (a = \'0\' and b = \'0\') then

sum<= \'0\' ;

cout<= \'0\';

else

sum<= \'0\' ;

cout<= \'0\';

end if;

end process;

endbasic_beh;

Data flow Modelling:

library ieee;

use ieee.std_logic_1164.all;

entity half_adder isport(a,b: in bit;s,c: out bit);

end half_adder;

architecture half_adder of half_adder is

begin

s<=(a xor b);

c<=(a and b);

end half_adder;

Homework Sourse

Homework Sourse