Give a highlevel view of pipelined processor datapath and ex

Give a high-level view of pipelined processor datapath and explain its working; compare the performance of pipelined datapath and the multi-cycle datapath.

Solution

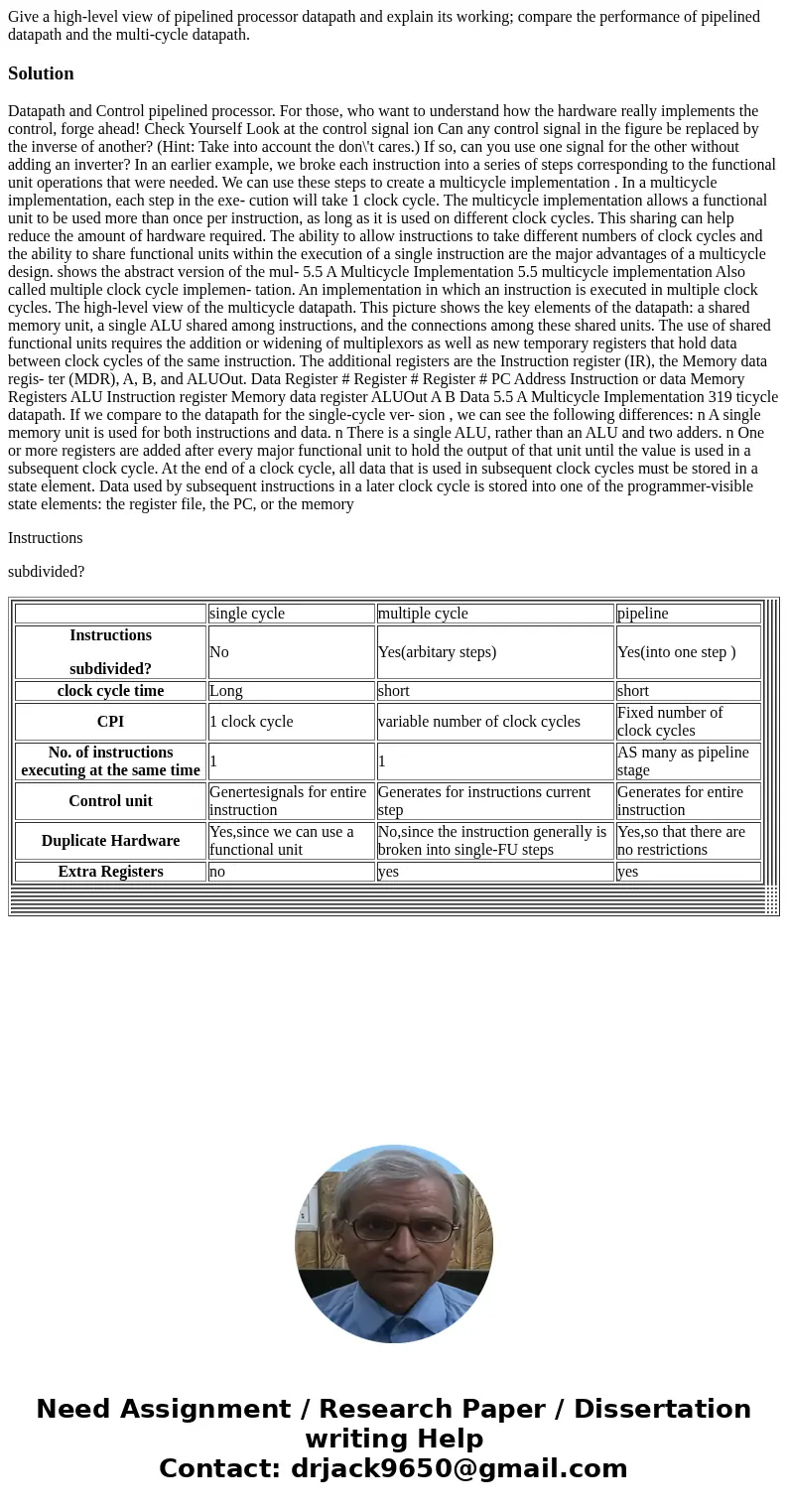

Datapath and Control pipelined processor. For those, who want to understand how the hardware really implements the control, forge ahead! Check Yourself Look at the control signal ion Can any control signal in the figure be replaced by the inverse of another? (Hint: Take into account the don\'t cares.) If so, can you use one signal for the other without adding an inverter? In an earlier example, we broke each instruction into a series of steps corresponding to the functional unit operations that were needed. We can use these steps to create a multicycle implementation . In a multicycle implementation, each step in the exe- cution will take 1 clock cycle. The multicycle implementation allows a functional unit to be used more than once per instruction, as long as it is used on different clock cycles. This sharing can help reduce the amount of hardware required. The ability to allow instructions to take different numbers of clock cycles and the ability to share functional units within the execution of a single instruction are the major advantages of a multicycle design. shows the abstract version of the mul- 5.5 A Multicycle Implementation 5.5 multicycle implementation Also called multiple clock cycle implemen- tation. An implementation in which an instruction is executed in multiple clock cycles. The high-level view of the multicycle datapath. This picture shows the key elements of the datapath: a shared memory unit, a single ALU shared among instructions, and the connections among these shared units. The use of shared functional units requires the addition or widening of multiplexors as well as new temporary registers that hold data between clock cycles of the same instruction. The additional registers are the Instruction register (IR), the Memory data regis- ter (MDR), A, B, and ALUOut. Data Register # Register # Register # PC Address Instruction or data Memory Registers ALU Instruction register Memory data register ALUOut A B Data 5.5 A Multicycle Implementation 319 ticycle datapath. If we compare to the datapath for the single-cycle ver- sion , we can see the following differences: n A single memory unit is used for both instructions and data. n There is a single ALU, rather than an ALU and two adders. n One or more registers are added after every major functional unit to hold the output of that unit until the value is used in a subsequent clock cycle. At the end of a clock cycle, all data that is used in subsequent clock cycles must be stored in a state element. Data used by subsequent instructions in a later clock cycle is stored into one of the programmer-visible state elements: the register file, the PC, or the memory

Instructions

subdivided?

| |||||||||||||||||||||||||||||||||||

Homework Sourse

Homework Sourse