redit is given without solution 1 Show the timing diagram of

redit is given without solution. 1. Show the timing diagram of the sequence of a 4-bit synchronous binary up/and counter if the clock and up/down control inputs have waveforms as shown below. The counter starts in the all-Os state and is positive edge- triggered. Qo is initially reset. (40 points) 112 HIGH F FFI LK Up DownDown Uptown-up-1 Down Down CLK Qi Q2 Q3

Solution

Sychronous counter ==> In synchronous counter each and every flip flop will be triggered by single clock at the same time.

UP counter==> In up counter we will increase the count bit on each clock pulse. Here one bit can be represented at one flip flop.

Down counter==> In down counter bit count is reduced at each clock. It is a reversible process of up counter.

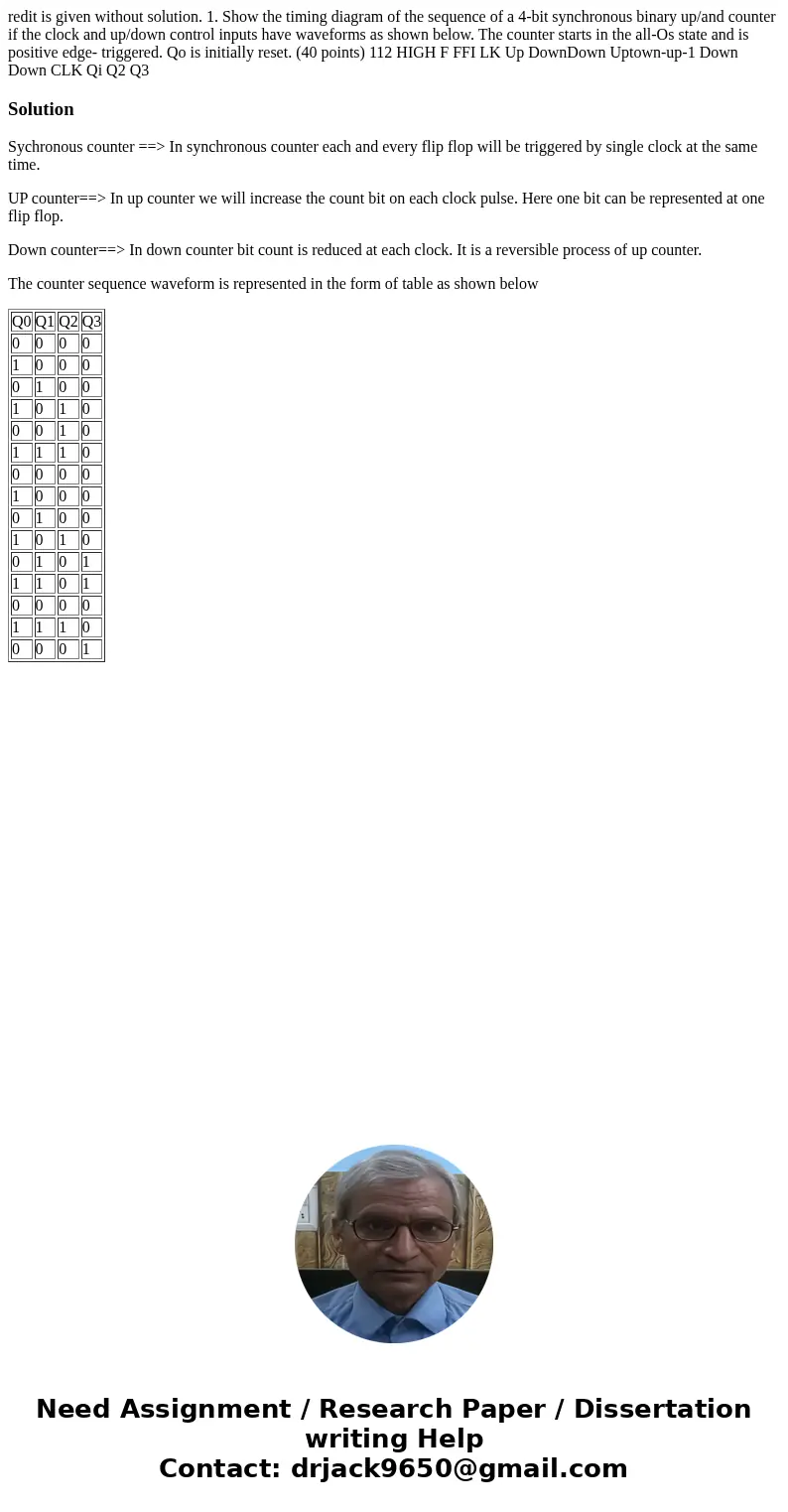

The counter sequence waveform is represented in the form of table as shown below

| Q0 | Q1 | Q2 | Q3 |

| 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 |

| 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 1 |

| 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 |

| 0 | 0 | 0 | 1 |

Homework Sourse

Homework Sourse