Diagram the stair step instruction execution for the followi

Diagram the “stair step” instruction execution for the following instructions. Assume no forwarding:

1

2

3

4

5

6

7

8

9

10

11

12

13

14

LW $t0, 0($s1)

IF

ID

EX

MEM

WB

ADDI $t3, $t0, 1

ADD $t1, $t3, $s0

SW $t3, 0($s1)

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | |

| LW $t0, 0($s1) | IF | ID | EX | MEM | WB | |||||||||

| ADDI $t3, $t0, 1 | ||||||||||||||

| ADD $t1, $t3, $s0 | ||||||||||||||

| SW $t3, 0($s1) |

Solution

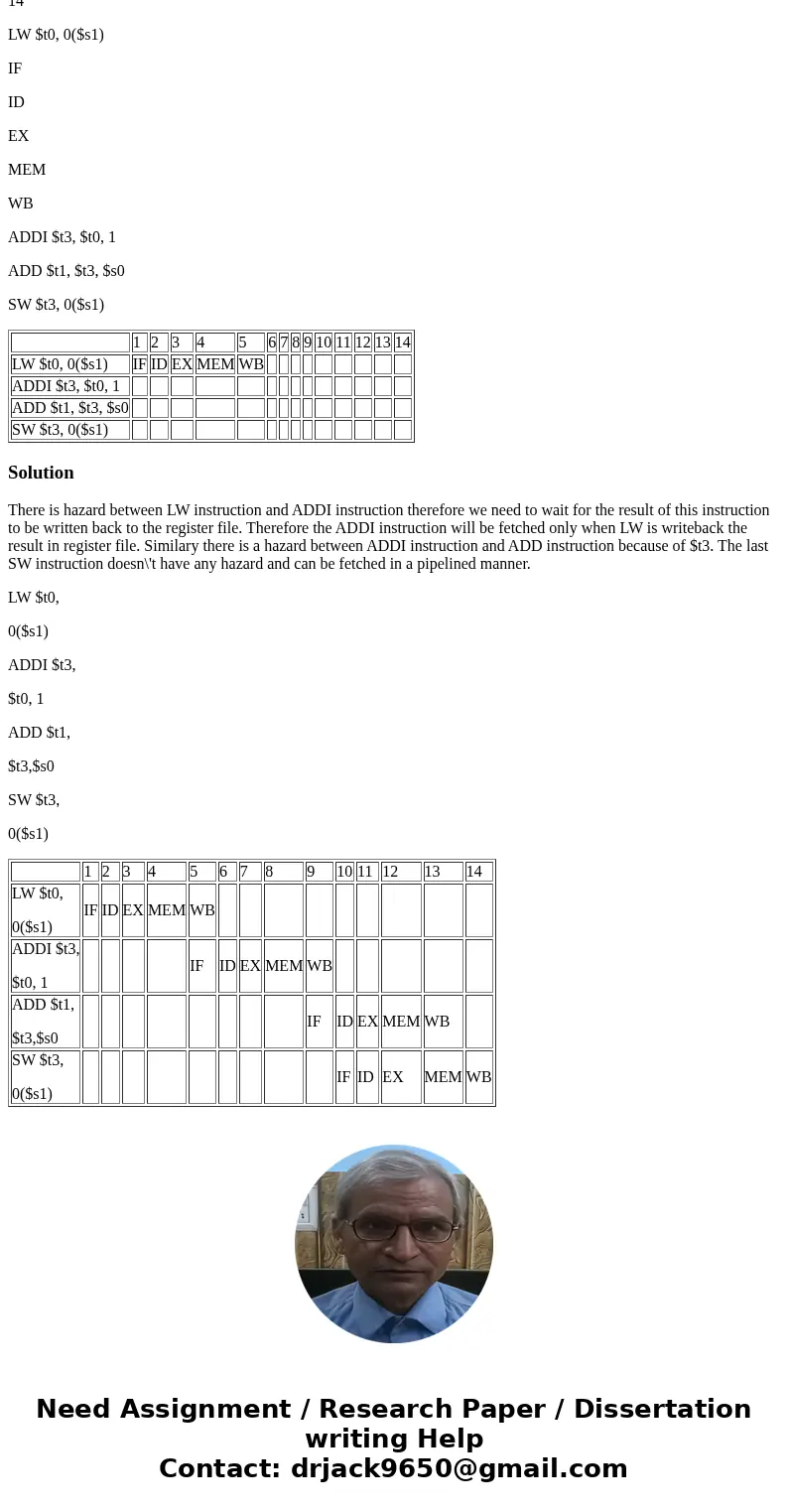

There is hazard between LW instruction and ADDI instruction therefore we need to wait for the result of this instruction to be written back to the register file. Therefore the ADDI instruction will be fetched only when LW is writeback the result in register file. Similary there is a hazard between ADDI instruction and ADD instruction because of $t3. The last SW instruction doesn\'t have any hazard and can be fetched in a pipelined manner.

LW $t0,

0($s1)

ADDI $t3,

$t0, 1

ADD $t1,

$t3,$s0

SW $t3,

0($s1)

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | |

| LW $t0, 0($s1) | IF | ID | EX | MEM | WB | |||||||||

| ADDI $t3, $t0, 1 | IF | ID | EX | MEM | WB | |||||||||

| ADD $t1, $t3,$s0 | IF | ID | EX | MEM | WB | |||||||||

| SW $t3, 0($s1) | IF | ID | EX | MEM | WB |

Homework Sourse

Homework Sourse