Following specifications The system has a 16bit address bus

Following specifications. The system has a 16-bit address bus, data bus, and READ and WRITE control signals. ROM starting at address constructed using 8K. times 4 chips of RAM starting at address 8000H constructed using 4K. times 8 chips n input port with no READY signal at memory-mapped address

Solution

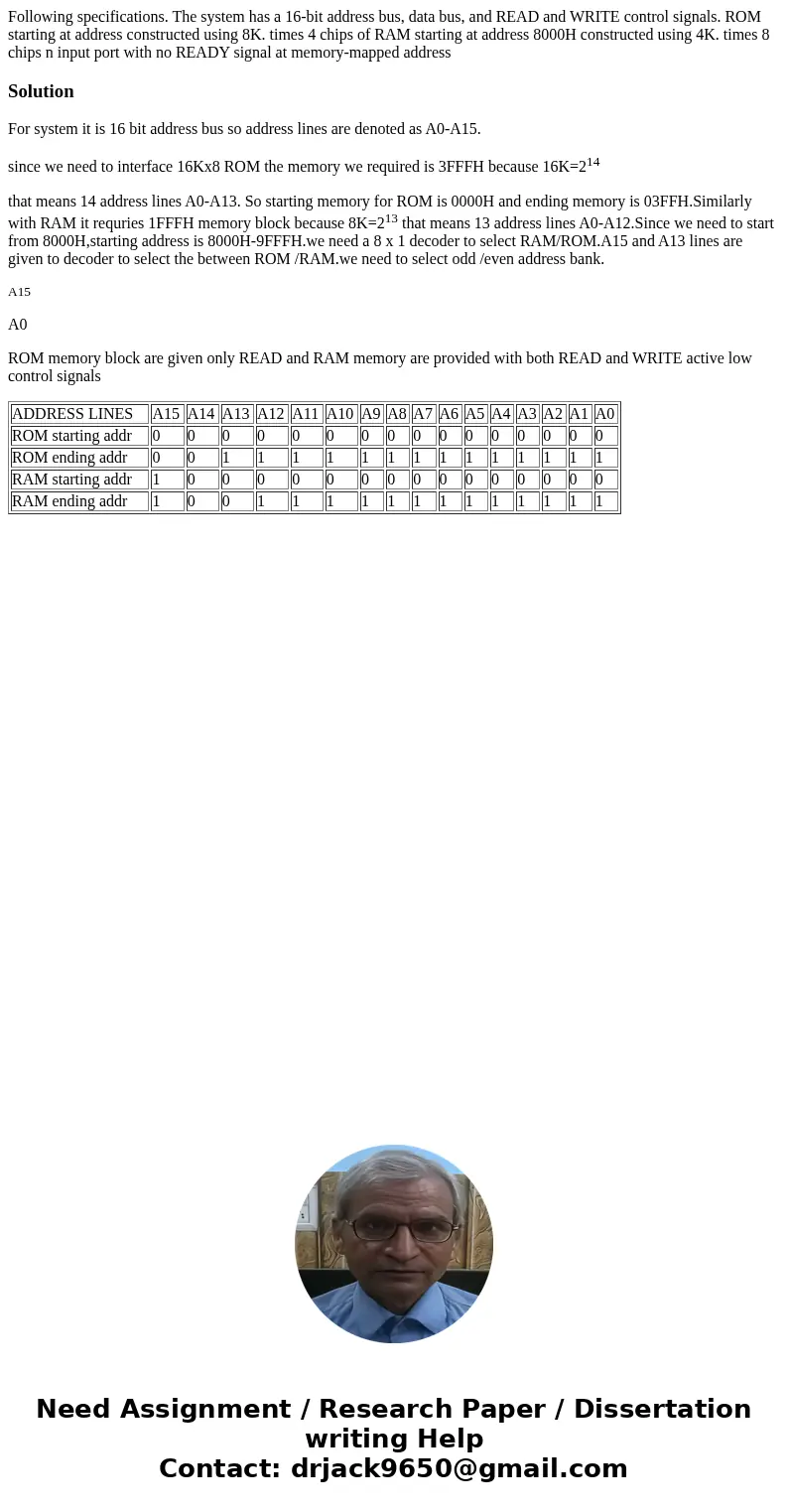

For system it is 16 bit address bus so address lines are denoted as A0-A15.

since we need to interface 16Kx8 ROM the memory we required is 3FFFH because 16K=214

that means 14 address lines A0-A13. So starting memory for ROM is 0000H and ending memory is 03FFH.Similarly with RAM it requries 1FFFH memory block because 8K=213 that means 13 address lines A0-A12.Since we need to start from 8000H,starting address is 8000H-9FFFH.we need a 8 x 1 decoder to select RAM/ROM.A15 and A13 lines are given to decoder to select the between ROM /RAM.we need to select odd /even address bank.

A15

A0

ROM memory block are given only READ and RAM memory are provided with both READ and WRITE active low control signals

| ADDRESS LINES | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

| ROM starting addr | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| ROM ending addr | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| RAM starting addr | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| RAM ending addr | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

Homework Sourse

Homework Sourse