Write a VHDL code based implementation of y x1 2x2 4x3 whe

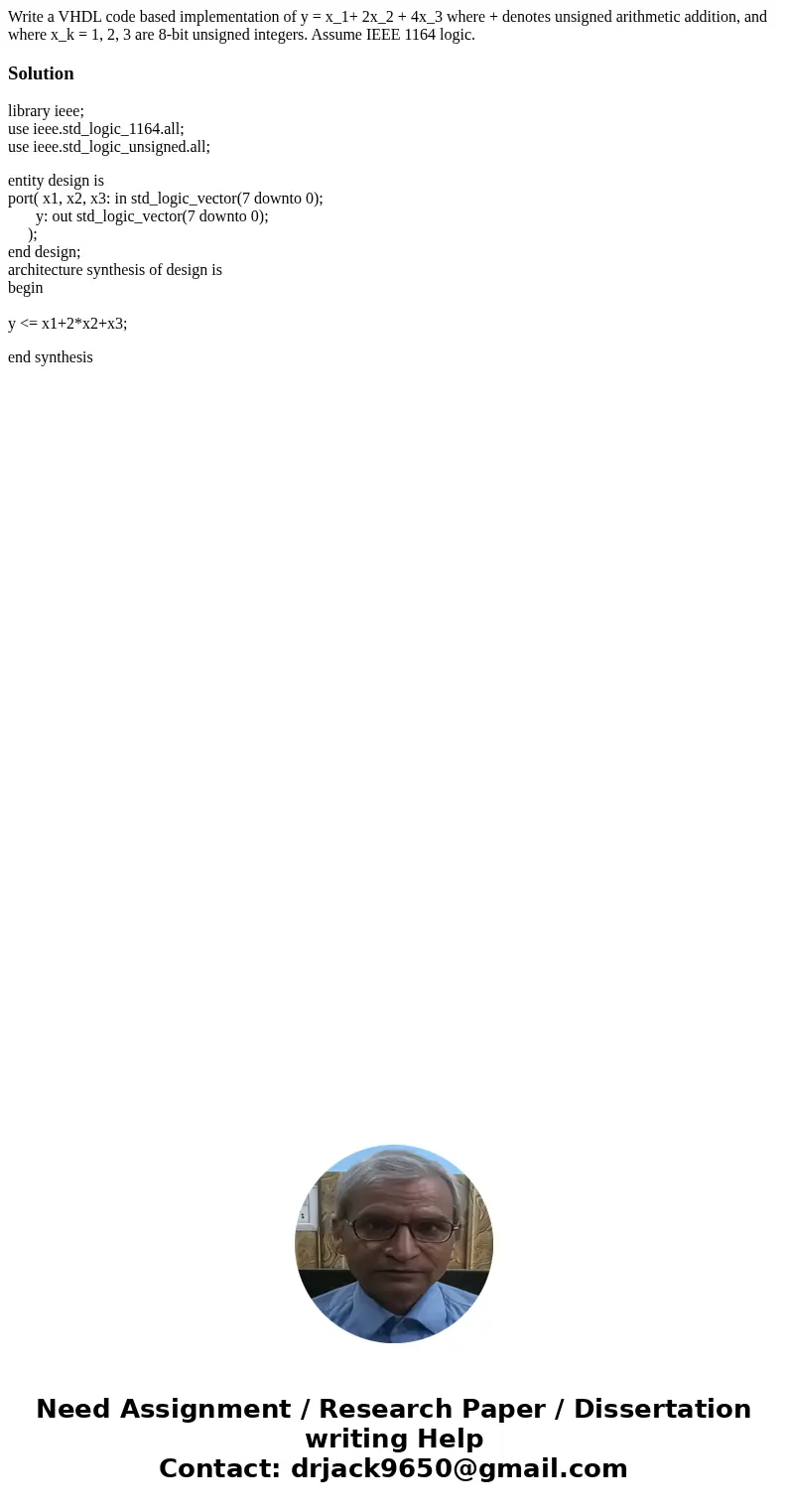

Write a VHDL code based implementation of y = x_1+ 2x_2 + 4x_3 where + denotes unsigned arithmetic addition, and where x_k = 1, 2, 3 are 8-bit unsigned integers. Assume IEEE 1164 logic.

Solution

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity design is

port( x1, x2, x3: in std_logic_vector(7 downto 0);

y: out std_logic_vector(7 downto 0);

);

end design;

architecture synthesis of design is

begin

y <= x1+2*x2+x3;

end synthesis

Homework Sourse

Homework Sourse